- 您现在的位置:买卖IC网 > Sheet目录2005 > LTC2143CUP-14#PBF (Linear Technology)IC ADC DUAL 14BIT 80 MSPS 64-QFN

19

21454314fa

LTC2145-14/

LTC2144-14/LTC2143-14

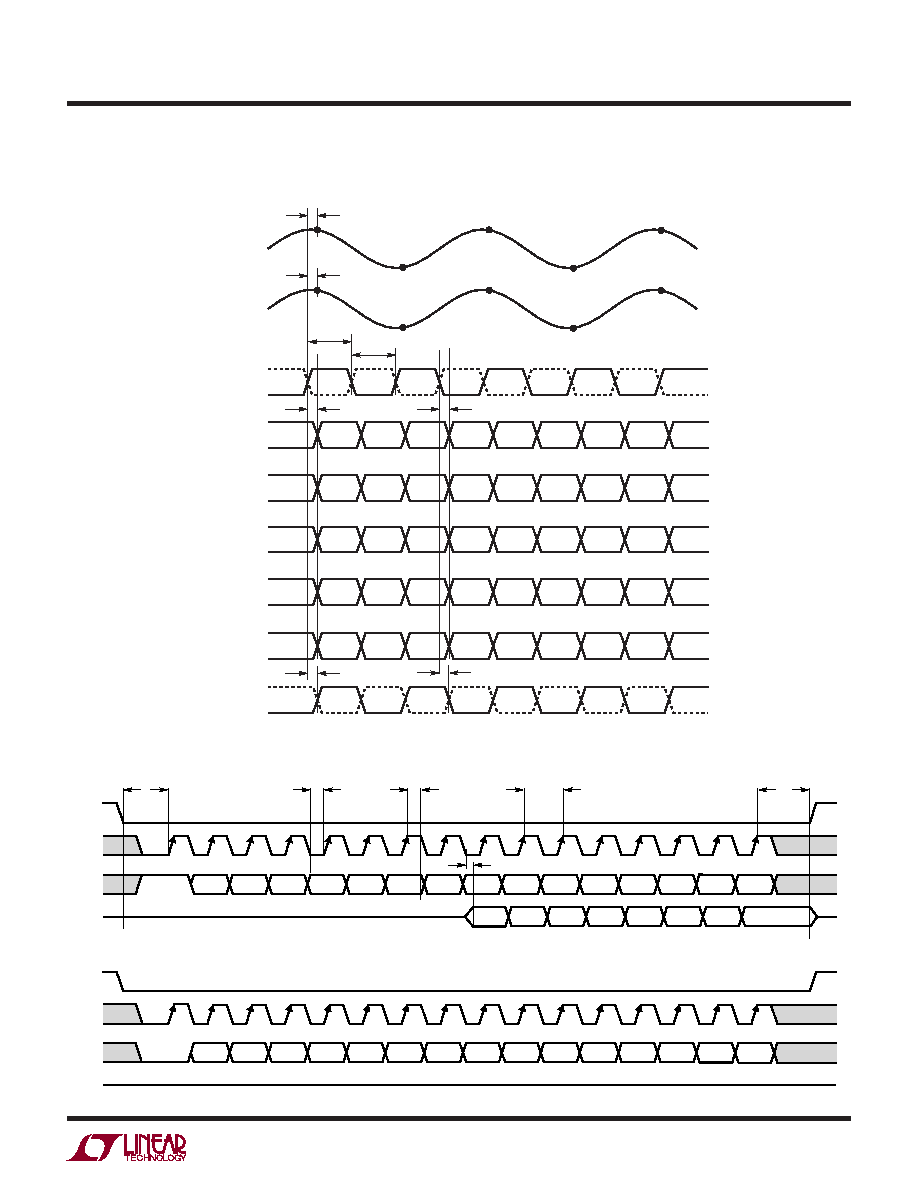

TIMING DIAGRAMS

Double Data Rate LVDS Output Mode Timing

All Outputs Are Differential and Have LVDS Levels

tD

tC

tL

BIT 0

A-6

BIT 1

A-6

BIT 0

A-5

BIT 1

A-5

BIT 0

A-4

BIT 1

A-4

BIT 0

A-3

BIT 1

A-3

BIT 0

A-2

BIT 12

A-6

BIT 13

A-6

BIT 12

A-5

BIT 13

A-5

BIT 12

A-4

BIT 13

A-4

BIT 12

A-3

BIT 13

A-3

BIT 12

A-2

ENC–

ENC+

D1_0_1+

D1_12_13+

BIT 0

B-6

BIT 1

B-6

BIT 0

B-5

BIT 1

B-5

BIT 0

B-4

BIT 1

B-4

BIT 0

B-3

BIT 1

B-3

BIT 0

B-2

BIT 12

B-6

BIT 13

B-6

BIT 12

B-5

BIT 13

B-5

BIT 12

B-4

BIT 13

B-4

BIT 12

B-3

BIT 13

B-3

BIT 12

B-2

OF

B-6

OF

A-6

OF

B-5

OF

A-5

OF

B-4

OF

A-4

OF

B-3

OF

A-3

OF

B-2

D2_0_1+

D2_12_13+

CLKOUT+

CLKOUT–

OF2_1+

D1_0_1–

D1_12_13–

D2_0_1–

D2_12_13–

OF2_1–

21454314 TD03

tH

tAP

A + 1

A + 2

A + 4

A + 3

A

CH 1

ANALOG

INPUT

tAP

B + 1

B + 2

B + 4

B + 3

B

CH 2

ANALOG

INPUT

A6

tS

tDS

A5

A4

A3

A2

A1

A0

XX

D7

D6

D5

D4

D3

D2

D1

D0

XX

CS

SCK

SDI

R/W

SDO

HIGH IMPEDANCE

SPI Port Timing (Readback Mode)

SPI Port Timing (Write Mode)

tDH

tDO

tSCK

tH

A6

A5

A4

A3

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

21454314 TD04

CS

SCK

SDI

R/W

SDO

HIGH IMPEDANCE

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

LTC2153IUJ-14#PBF

IC ADC 14BIT DUAL 310MSPS 40QFN

LTC2158IUP-14#TRPBF

IC ADC DUAL 14BIT 310M 64-QFN

LTC2172IUKG-14#TRPBF

IC ADC 14BIT SER/PAR 65M 52-QFN

LTC2175IUKG-14#TRPBF

IC ADC 14BIT 125MSPS QUAD 52QFN

LTC2202IUK#TRPBF

IC ADC 16-BIT 10MSPS 48-QFN

LTC2205IUK-14#PBF

IC ADC 14BIT 65MSPS 48-QFN

LTC2207IUK-14#PBF

IC ADC 14BIT 105MSPS 48-QFN

LTC2220IUP-1#TRPBF

IC ADC 12BIT 185MSPS 64-QFN

相关代理商/技术参数

LTC2143CUP-14#TRPBF

功能描述:IC ADC DUAL 14BIT 80 MSPS 64-QFN RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极

LTC2143IUP-12#PBF

功能描述:IC ADC DUAL 12BIT 80MSPS 64-QFN RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极

LTC2143IUP-12#TRPBF

功能描述:IC ADC DUAL 12BIT 80MSPS 64-QFN RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极

LTC2143IUP-14#PBF

功能描述:IC ADC DUAL 14BIT 80 MSPS 64-QFN RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极

LTC2143IUP-14#TRPBF

功能描述:IC ADC DUAL 14BIT 80 MSPS 64-QFN RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极

LTC2144-12

制造商:LINER 制造商全称:Linear Technology 功能描述:12-Bit, 125Msps/105Msps/ 80Msps Low Power Dual ADCs

LTC2144-14

制造商:LINER 制造商全称:Linear Technology 功能描述:12-Bit, 125Msps/105Msps/ 80Msps Low Power Dual ADCs

LTC2144CUP-12#PBF

功能描述:IC ADC DUAL 12BIT 105MSPS 64-QFN RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极